2023汽车半导体生态峰会 || 泰瑞达冯水忠:车规芯片测试的发展

以“链启芯程·智造未来”为主题的“2023汽车半导体生态峰会暨全球汽车电子博览会”,由广东省工业和信息化厅、深圳市工业和信息化局、中国能源汽车传播集团指导,《中国汽车报》社主办,爱集微承办,于2023年9月26日至27日在深圳福田会议中心隆重召开。

本届峰会坚持行业领袖峰会的高端定位,全面助力产业间深度融合与创新,推动上下游产业链伙伴携手合作,共同构建具有全球竞争力的汽车科技创新新生态。

峰会现场,多领域、多视角开展的20场特色活动,囊括主峰会、技术研讨、项目路演、专业展览、交流盛宴等,汇聚政、产、学、研、用、投等多个产业圈层,围绕全球及中国汽车半导体产业热点展开交流,峰会重点聚焦新技术、新趋势,深入剖析汽车半导体各细分领域的发展机遇和挑战,近百个精彩纷呈的演讲,共同呈现出一幅专业而全面的思维图景。

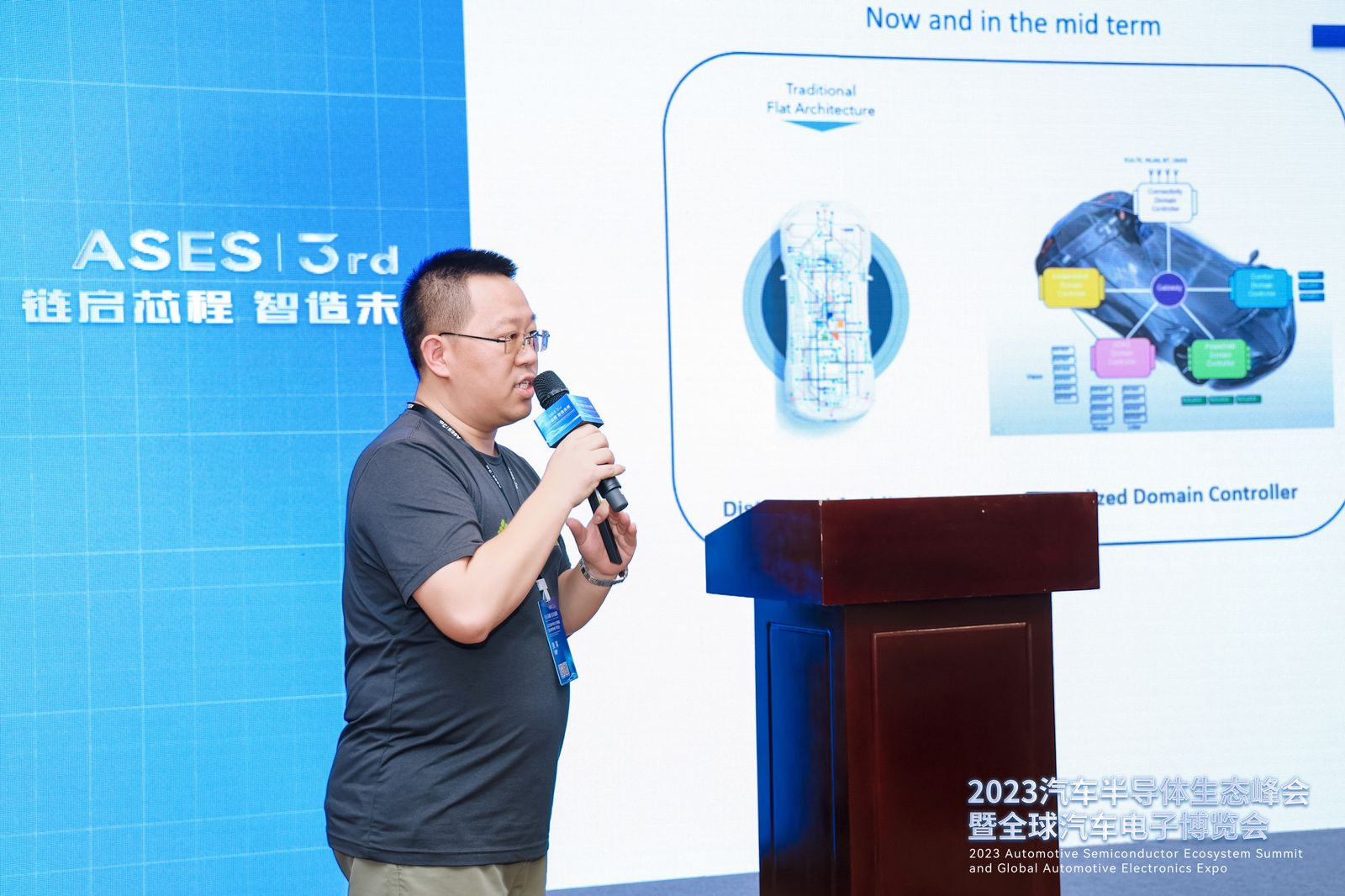

其中,在9月26日举办的“汽车电子部件及车规级芯片专场”,泰瑞达上海有限公司业务经理冯水忠,做了题为《车规芯片测试的发展》的精彩演讲。以下内容为现场演讲实录:

冯水忠:非常荣幸爱集微请我们来,大家有机会欢聚在一起,谈谈整个中国的车规半导体以后的发展。泰瑞达是专门做芯片测试解决方案的,整套流程都有,从测试的芯片CP,FT到SLT都有成熟的解决方案,今天我们从这个角度非常浅尝即止的理解车规芯片在测试这一块的发展。

泰瑞达上海有限公司业务经理 冯水忠

首先看目前车规市场的概况。两个维度,第一汽车能源结构,这张图可以看得非常清楚,传统的能源汽车和混合动力汽车、纯电汽车,虽然未来几年汽车市场整体的增长只有2%,但是混合或纯电动汽车的增长率可以达到16%,第二自动驾驶,其中ADAS芯片是所有车规芯片的重中之重。发展趋势进本从L1一直到L5,随着芯片迭代,芯片的制程复杂程度和测试需求也会随之提高,这也会带动整个汽车行业往前跑。

总之,传统的能源型汽车和纯电汽车,半导体含量的部分会越来越多,而且车规芯片增长势必会驱动整个行业发展。5G,AI和 车载芯片是最近几年引领半导体技术发展的三大方向,车规芯片中电子/电气和自动驾驶又是主要的两个因素。

电气和电子化,怎么去看这个问题?从车的结构发展方向来看,由分布式 ECU 向域控制/中央集中架构方向发展,主要分为三种方式:分布式(模块化→集成化)、 域集中(域控制集中→跨域融合)、 中央集中式(车载电脑→车-云计算)。传统的汽车一般都是以ECU为主体的分布式结构,当下的电车都是以功能域即根据功能划分的域控制器,最常见的是如博世划分的五个功能域(动力域、底盘域、车身域、座舱域、自动驾驶域)。域控制器间通过以太网和 CANFD(CAN with Flexible Data-Rate)相连,在功能域基础上,为进一步降低成本和增强协同,出现了跨域融合,即将多个域融合到一起,由跨域控制单元进行控制。从而将五个功能域(自动驾驶域、动力域、底盘域、座舱域、车身域)过渡到三个功能域(自动驾驶域、智能座舱域、车控域)。最终实现分布式处理,在每一个区域都具有着非常大量的内容,而他们之间是通过一些先进的协议去做的,这种发展趋势可以细分一下。传统的分布式架构带来的弊端是什么?第一、ECU非常多,第二ECU单元线束非常多,非常长,而且不同的ECU单元,因为每个功能商都根据自己的区域去设计的,所以同步、垂直孤岛式开放,需要非常多的供应商支持。整合统一化做得非常的弱,也不利于整个车芯片往前发展。不同的ECU框架平台不一样,OTA升级困难;但是中央计算平台区域接入+中央计算保证了整车架构的稳定性和功能的扩展性,新增的外部部件可以基于区域网关接入,硬件的可插拔设计支持算力不断提升,充足的算力支持应用软件在中央计算平台迭代升级。

半导体元器件在整个车上,无论从架构上还是占比趋势上,基本上到2030年,可以占到一半。归类到三大块:ADAS,电气,智能驾舱,智能语言。整个车规级芯片年复合增长率到2029年是16%,电气化20%,ADAS 14%,娱乐通信这一块是8%。

ADAS分为L1到L5五个阶段,L1就是辅助,不叫自动。L2是部分自动,比如自适应巡航,L3是有条件的自动驾驶,L4能实现自动泊车和城市自动驾驶;L5就是终极理想,全方位自动驾驶。

在L1到L2或者L2+的时候,主要的玩家还是传统的车厂,以主机厂为导向,但从测试的角度看,复杂度还不是太高,到L2测试相对难一些,复杂度设计可能只有6到8倍,但到了L3、L4,会发现玩家变了,非常高阶的芯片玩家介入了,会有专门有一些专业级的芯片设计公司去做这个事,而且测试的复杂度不是一般,基本上是10~50倍的增减。

因此,今后5到10年,车规市场将会影响整个半导体行业。其中考量车规芯片最重要的一个指标就是质量。为什么是质量第一位?人的生命拥有是第一位的。这些车规芯片为什么要求质量这么高?一个案例,2015年,日本一家安全气囊的公司出现问题,让相关企业都付出巨大的代价:召回、罚款,而且影响时间长,从2002到2015年,后续还有很多赔偿。所以,不能在质量上犯任何错误,特别是安全等级越高的产品,基本上是毁灭级的,所以质量是第一位。怎么做到质量第一位?可能需要同仁包括一些行业的标准去规定。这里简要概述测试方面的需求,芯片从出生到最后售后,每个芯片从出生开始,做技术文档论证的时候,就要考虑很多因素,比如产品的封装形式、电压范围、温度范围,包括产品的晶体管的耐受力,还有一些存储芯片回读性等,这些都是前期能看到的;真正设计的时候,要考虑更多的东西。每一个节点必须遵守行业三大标准:功能安全验证ISO26262,测试规范认证AECQ100,覆盖整个链路的质量体系认证TS/ISO16949。

行业的趋势和挑战有哪些?首先,车载电子产品普及率大幅提高:看看中国的发展就知道,特别是从18年到现在,基本上过去十年翻了将近一番,还是比较保守的,有报告显示,可能不止这么多;定制的IC取代通用产品;每个芯片的测试项目数量和复杂性不断增长:包括刚刚说的摄像头、诊断、ADAS信息娱乐等这种需求越来越多,还有自动驾驶,要满足一些功能安全的时候,必须有一些非常冗余的电路设置,还要求芯片的算力很高,仪表板显示控制台演变为计算机化神经中枢;兼容性和开放架构的需求:车载网络必须可扩展,支持多个系统和设备,网络需要聚合能力,汽车制造商需要开放架构;线束限制:汽车制造商寻求成本更低的布线方式;行业标准要求:车载技术必须满足严格的法规,可靠性、温度、最低功耗,标准更加细化严格,更宽广度和深度;最后是传输带宽挑战:更多数据需要更高的传输速率,例如以太网,V2X和OTA,

芯片质量由三个因素决定:故障模型质量,故障覆盖率和环境缺陷的激活条件,考虑到这些因素,目标是将缺陷降低至 0 DPPM。车规芯片要求测试产品规格书列出所有项目都必须覆盖。除此之外车规芯片都需要进行三温测试,跟不同温度环境下的表现决定了芯片的等级。为了能满足这些需求芯片厂商需要采用新的技术推动,且必须考虑成本和质量。在拥挤的赛道中尽快把产品上市。因此也会带来一些思考:新技术的可靠性好不好?包容性强不强?测试和研发的速度能不能快速衔接,产品的数据链路怎么打通?泰瑞达在这个行业做得比较久的,永远是技术优先,我们在整个行业,特别是在海外这个行业,有很多专业的知识可以提供给本地的客户分享,让大家了解别人是怎么做的。

这里列了一下,目前泰瑞达已经有提供方案给到这些非常著名的头部客户。除了这些以外,下面还有很多。泰瑞达在整个车规芯片数字市场MCU,包括SOC、ADAS、智能驾舱,top8的基本上都有一些产品在用,其中5个,大部分都是用泰瑞达的产品,其中6个是用了最新的平台,主要还是操作于SOC的芯片,一个大平台。最边上是泰瑞达的市场份额占比,占55%左右,AEC成员大部分芯片公司都有在泰瑞达平台上量产。

泰瑞达怎么做车规级芯片的测试?

从生态链来看,从CT到FT,再到SLT,每个测试站点着重点是不一样的。泰瑞达能做一个全覆盖,从CP到FT到SLT,前几年推出的SLT系统(Titan),是针对AP处理器,可以做到424个工位并行测试,产出非常高,高通等一些大厂已经在用了。满足客户成本和质量的平衡,既能保持质量,又能对成本有所提高,降本增效。

芯片测试对成本影响最大的就是要尽快发现产品的缺陷在哪。在最早的阶段就是CP阶段发现并筛除,这样减少后面的损耗。还有减少对后续生产力提升的影响,产品必须是保质保量的,没有任何测试问题的。通过测试,能不能反向推动前面的一些设计,这个都是相辅相成的,最后才能得到一个极致的产品。泰瑞达在2019年面向市场推出了一款最新的Soc测试平台:ULtraFLEX Plus,具备三大特点:

大数字:既能满足单site的大数字管脚需求还能兼顾多site的测试

高功率:单通道提供2560A的电流,动态响应稳定,静态供电精准

易学习:统一的IG-XL的编程环境,确保工程师快速上手大数字,高功率,易学习。

主要依托于以下的设计:

• 全新测试头容纳2X以上密度的测试资源

• IGXL 软件架构完全向上兼容

• 扩大3x 应用电路面积(1600 cm²),确保工位间的走线高度一致性的硬件设计

• 可降低50%多工位运算传输开销的,全新的分布式处理器架构提高运算效率

• 可升级基础架构,可以延长设备寿命

• 20-30% 更低的功耗

推出了三种配置:Q6(6个槽位),Q12(12个槽位)和Q24(24个槽位),Q6最大可以拥有3K的数字资源,Q12达到6K的数字资源。同时考虑实际应用中考虑电源的使用,Q6能提供900A的负载能力,Q12最多可以提供1900A的负载能力。综合产品的需求,都可以灵活选择相应的配置。

针对市场的需求,泰瑞达推出了高性能的第三代资源组合:

UltraPin2200 +(高密度)

新一代数字板卡

• 高密度,单板卡支持512个数字通道

• 单板支持32组向量生成器适用于高并测试需求,不同site实现不同向量测试

• 专有的、基于硬件的协议感知能力

• 独立的非确定性收发向量储存器

• 高达57.6Gb 向量的16通道间任意分享测试向量深度

• PACE架构实现“0” 开销数据处理

• 高精度PPMU(MV to ±1mV),进行PerPin频率,抖动以及时间延测量

UVS64 (大电流)

新一代大电流电源板卡

• 非常准确,稳定的资源为芯片核心供电: 64通道@5A

• 业界顶尖的动态响应能力(<55 mv@2560A)

• 400uV 6 Sigma 静态电压精度

• 单板提供320A的供电能力

• 板级并联实现2560A的巨大的供电能力

• 自动软件报警能力,确保测试质量

• 电流双钳位功能,保证上电安全和毛刺检测功能

• 可调的上电斜率和AWG功能

UVS256-HP (多通道)

高密度、高度灵活的通用电源板卡

• 256通道每个仪器

• 灵活的合并能力

• 卓越的动态性能

• 低噪音

• 四象限电压或电流源和测量

UVI264(更灵活)

高精度、高密度直流VI源

• 248个低压通道:-2V~+8.5V@2A

• 16个高压通道:-50V ~+90V@2A

• 灵活的通道合并

• 高精度差分测量单元(24 位ADC)

UltraCTO384 (高产出)

高性能,高密度转换器测试选项

• 128个源通道,128个捕获通道和128个参考通道

• 集成精密源校准电压基准 最大偏置误差: 75uV, 增益误差 20ppm (~17 bit)

• 从直流线性度道交流噪声的全套测试应用开发模板,大幅度加速程序开发

• 测试向量同步控制保证精密的时序以及可重复性

• 单板卡无继电器即可保证128工位同步测试

开发环境也是泰瑞达产品的有一大优势,IG-XL 软件是专为质量和兼容性而打造。如果你熟悉Windows,熟悉Excel,开发任务非常简单,基本上这个软件已经超过了15年,20年了,保持15年以上的兼容性,假如你一开始就学这个软件,你到了现在,15年以后你累计的经验是对你有帮助的。VLSI调研得出IGXL被客户评价最佳用户体验软件。IG-XL基础库可重复使用, 在平台移植过程中大大减少工程师的工作量。截止到目前,UltraFlex Plus整个产业到650台装机。

最后再强调一点,就是生态不只是测试链路的生态,还有前期跟EDA软件的融合,通过portbridge测试跟EDA软件做相互融合,打破DFT和测试技术墙,能让DFT工程师直接通过EDA的软件在测试机上调试,加快向量迭代和数据收集。快速找出芯片中发生的事情,调试时间大大缩短。需要数周时间才能解决的问题可以在数小时内解决,尤其是需要在不同时区进行远程调试的问题。

泰瑞达与第三方合作广,基本上市场上有的分选机,探针台,各种治具品牌,都跟泰瑞有深度合作,一次整个量产生态不用去担心,都能满足需求,到这里我今天就讲完了。大家感兴趣可以来咨询一下,泰瑞达在深圳也有点,特别在全国的是在半导体非常活跃的城市,都会对应的支持团队。

谢谢大家。